# 数字集成电路原理

# 课堂讨论3

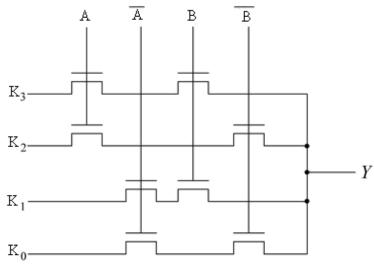

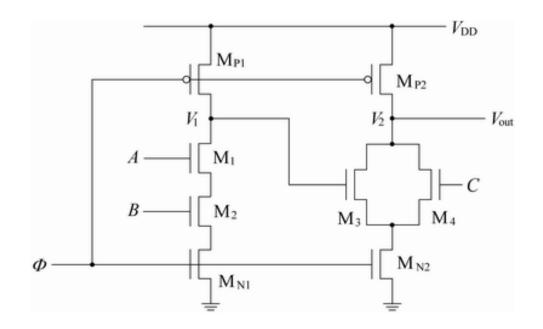

分析如下电路在各种输入状态下的 $K_{\text{Neff}}$ 和 $K_{\text{Peff}}$ ,确定电路的直流噪声容限,假定所有MOS管的阈值电压绝对值都是 $V_{\text{T}}$ ,导电因子都是K。

# 讨论题2-3

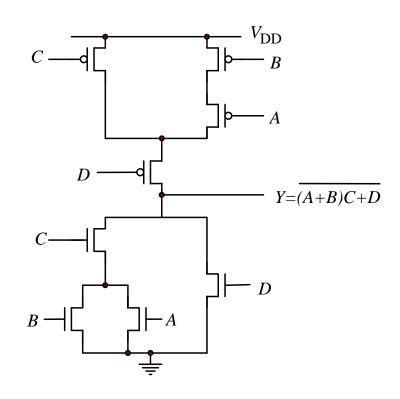

2、如何实现下述逻辑功能,画出对应的静态CMOS电路。

$$Y = \overline{AC + BD + ADE + BCE}$$

3、若所有输入信号的高电平是VDD,低电平是 0 ,所有MOS管的阈值电压是VT,导电因子是K,分析传输门阵列的输出高、低电平以及传输延迟时间。

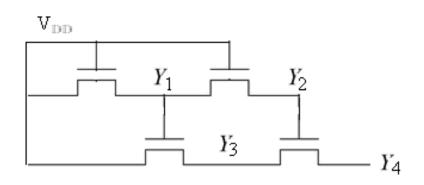

4、分析下图电路中各节点的电压,近似分析Y4的传输延迟时间。

5、在保证功能不变的前提下,如何改进如下电路, 使电路能可靠工作。

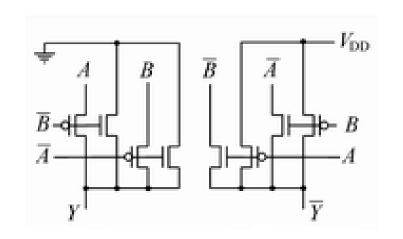

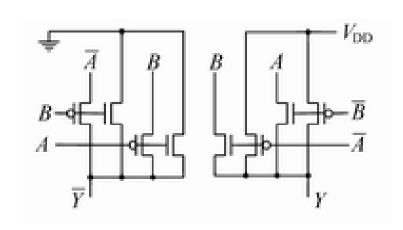

6、分析如下DPL电路的逻辑功能和高、低电平。

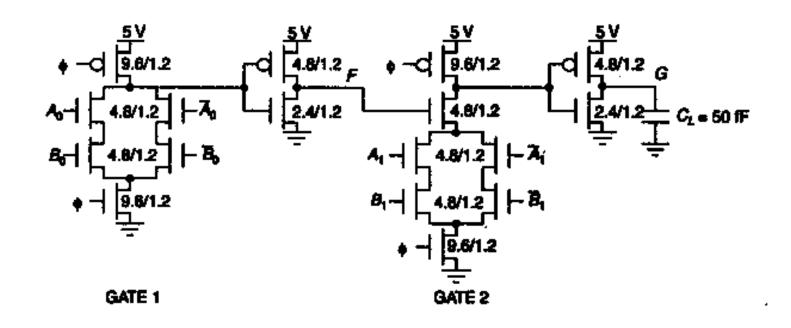

下图是2级多米诺电路,分析电路中F和G的逻辑功能,并分析F和G的输出哪一个更易受到电荷分享的影响,近似分析从输入到G的传输延迟时间。

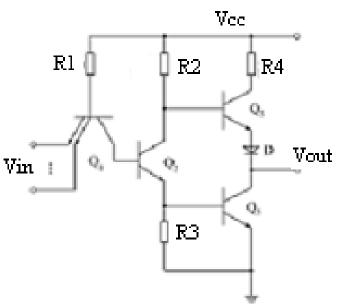

如图一个TTL电路,已知*R2/R3* = 1.6,//L = 1.6mA,输出低电平时电源电流为5.5mA,输出高电平时电源电流为2 mA,电源电压为5V,VBE(on)=0.8V考虑电阻的制造误差为20%,电源电压有10%的波动,设计*R*1、*R*2和*R*3的标称值。